行业动态

-

如今,各种便携式计算设备都应用了密集的印刷电路板(PCB)设计,并使用了多个高速数字通信协议,例如 PCIe、USB 和 SATA,这些高速数字协议支持高达 Gb 的数据吞吐速率并具有数百毫伏的差分幅度。设计人员必须小心的规划 PCB 的高速串行信号走线,以便尽可能减少线对间串扰,防止信道传输对数据造成破坏。

2018-07-24 13:53:57 技术文档

了解详情 -

随着电路板抄板(PCB抄板)出现新的部分加成法(semi-additive)技术,可让其布线(trace)宽度减为一半达到1.25mils水准,因此,可让电路装配密度达到最大。据EETimes网站报导,目前积体电路不断进步已从过去在半导体IC微影制程(Lithography)上,开始转移到PCB制程上。 目前业界最常用的减成法(subtractive)PCB制程,其布线宽度容忍公差最小可达到0.

2018-07-24 13:52:03 技术文档

了解详情 -

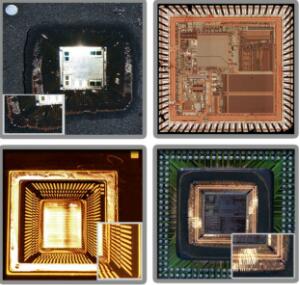

芯片解密开封, 即开盖/开帽, 指去除ic封胶, 同时保持芯片功能的完整无损, 保持 die, bond pads, bond wires乃至lead-frame不受损伤, 为下一步芯片失效分析实验做准备。

2018-07-24 13:50:46 技术文档

了解详情

友情链接: